# THE WIDE-BAND AMPLIFIERS μPG100B/μPG101B

# 1. GENERAL

$\mu$ PG100B/101B is the GaAs MMIC (GaAs Microwave Monolithic Integrated Circuit) developed as the low noise wide band amplifier/medium power wide band amplifier.

$\mu$ PG100B features NF of 3 dB or less and power gain of 15 dB from 50 MHz to 3 GHz, and  $\mu$ PG101B features  $P_{O(1 \text{ dB})}$  (output power at 1 dB gain compression point) of about 17 dBm and power gain of 13 dB in the same frequency band.

These ICs are suitable for IF stages of microwave communication system and the measurement equipment which require low noise and the medium power characteristics respectively.

This data sheet introduces the characteristics and applications of these ICs.

### 2. INTERNAL EQUIVALENT CIRCUIT

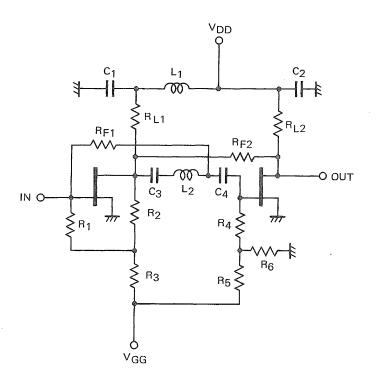

Fig. 1 shows the internal equivalent circuit of  $\mu$ PG100B/101B.

Fig. 1  $\mu$ PG100B/101B Equivalent Circuit Diagram

As the circuit configuration, the single end type which consists of two stages of GaAs FET with a gate length of 0.8  $\mu$ m and a gate width of 1 mm is utilized. To realize the wide band characteristic, both the first and second stage FETs are provided with negative feedback by feedback resistors R<sub>F1</sub> (for the first stage) and R<sub>F2</sub> (for the second stage), respectively. (Only the second stage FET for  $\mu$ PG100B has the gate width of 500  $\mu$ m).

The operating currents for the first and second stage FETs are set as shown in Table 1. The second FET stage of  $\mu$ PG101B is biased by a relatively large bias current of 55 mA to get high output power.

Because of the large bias current it is required to put choke coil in parallel with load resistor  $R_{L2}$  to prevent  $V_{DS}$  from getting down.

Table 1 Internal FET Operating Current Values

(Unit: mA)

|         | First Stage | Second Stage |

|---------|-------------|--------------|

| μPG100B | 25          | 20           |

| μPG101B | 40          | 55           |

#### 3. DEVICE CHARACTERISTICS

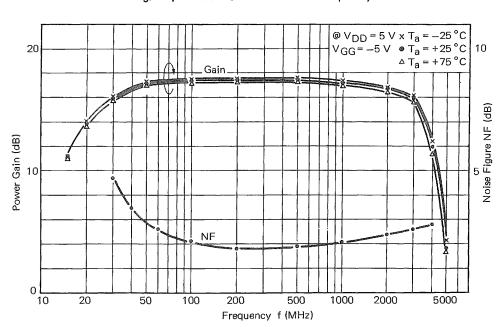

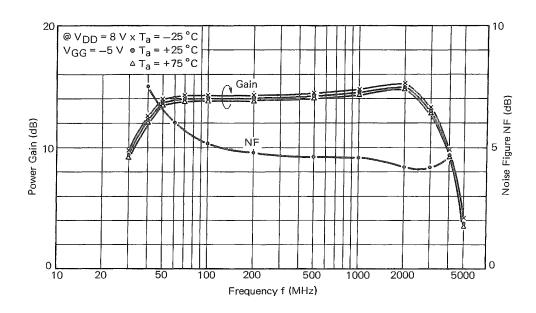

Fig. 2 and 3 show the Gain and NF versus frequency characteristics for  $\mu$ PG100B and  $\mu$ PG101B, respectively. Both devices have extremely good temperature characteristics of the gain variation, which is approximately about 0.5 dB (0.005 dB/°C) within the ambient temperature range from -25 to +75 °C.

$\mu$ PG100B features NF of 3 dB or less from 50 to 3 000 MHz and  $\mu$ PG101B features NF of 6.5 dB or less within the same band.  $\mu$ PG100B is especially suitable for a low noise, wide band amplifier.

Fig. 2 µPG100B Gain and NF vs. Frequency

Fig. 3  $\mu$ PG101B Gain and NF vs. Frequency

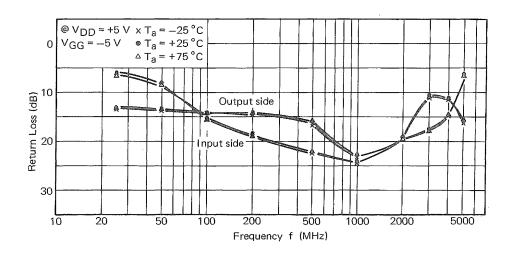

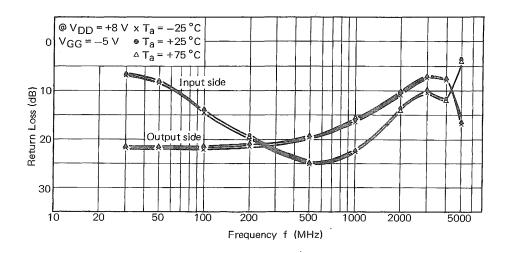

Fig. 4 and 5 show input/output return loss versus frequency characteristics as a function of temperature for  $\mu$ PG100B and  $\mu$ PG101B, respectively.

Fig. 4 μPG100B Return Loss vs. Frequency

Fig. 5 μPG101B Return Loss vs. Frequency

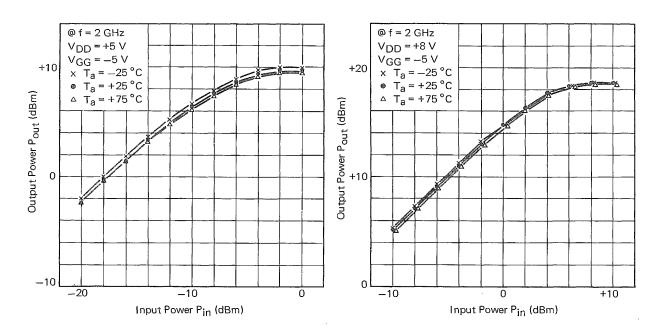

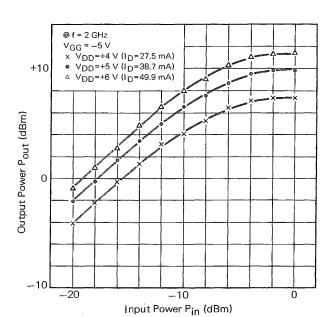

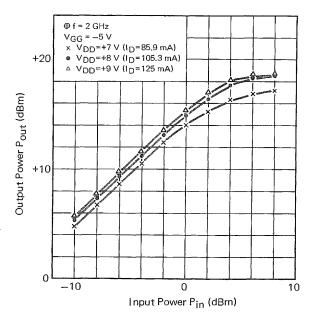

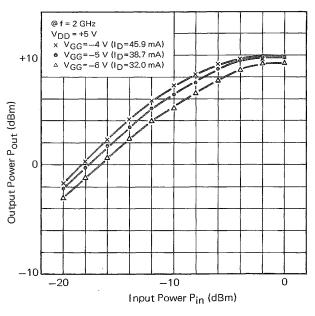

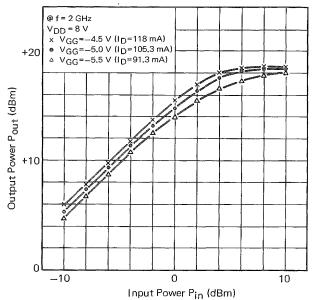

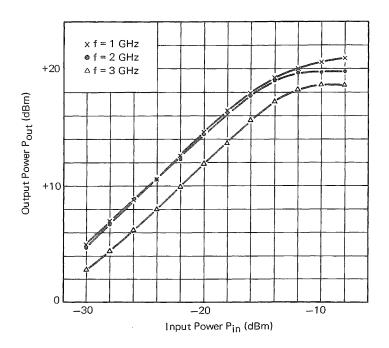

Fig. 6 through 11 show the temperature and the supply voltage dependency of  $P_{in}-P_{out}$  for  $\mu PG100B$  and  $\mu PG101B$ .

The output power at 1 dB gain compression point,  $P_{O(1 \text{ dB})}$ , is +7 dBm for  $\mu$ PG100B and +17 dBm for  $\mu$ PG101B (@. f = 2 GHz).  $\mu$ PG101B is suitable for a medium output power, wide band amplifier. As for the temperature characteristics of both  $\mu$ PG100B and  $\mu$ PG101B,  $P_{O(1 \text{ dB})}$  varies about 0.5 dB (0.005 dB/°C), which is almost the same as gain variation.

As for the supply voltage dependency of  $P_{O(1\ dB)}$ ,  $\mu PG100B$  has 2 dB/V on the  $V_{DD}$  side and 1 dB/V on the  $V_{GG}$  side;  $\mu PG101B$  has 1 dB/V on the  $V_{DD}$  side and 0.8 dB/V on the  $V_{GG}$  side.

For practical use, the 3-pin regulator is recommended to be used for stabilizing the supply voltage to prevent the characteristic from changing caused by supply voltage variation.

Fig. 6 μPG100B Pout-Pin Characteristic

Fig. 7 μPG101B P<sub>Out</sub>-P<sub>in</sub> Characteristic

Fig. 8  $\mu$ PG100B  $P_{out}$ - $P_{in}$  Characteristic

Fig. 9  $\mu$ PG101B P<sub>out</sub>-P<sub>in</sub> Characteristic

Fig. 10  $\mu$ PG100B  $P_{out}$ - $P_{in}$  Characteristic

Fig. 11  $\mu$ PG101B  $P_{out}$ - $P_{in}$  Characteristic

# 4. APPLICATIONS

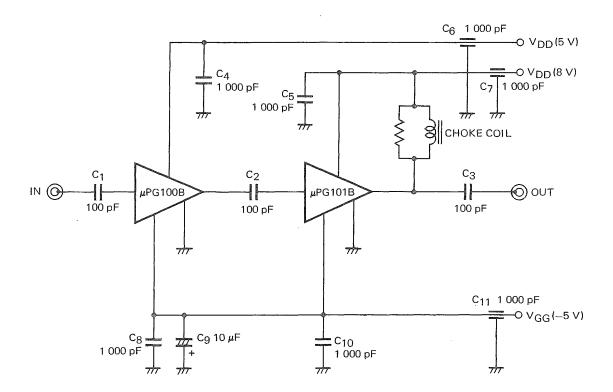

When these ICs are practically used, generally these are cascaded and used as multi-stage amplifiers. In this case, the first stage requires the low noise characteristic, and the second stage requires linearity. Here, the amplifier using  $\mu$ PG100B for the first stage and  $\mu$ PG101B for the second stage is introduced.

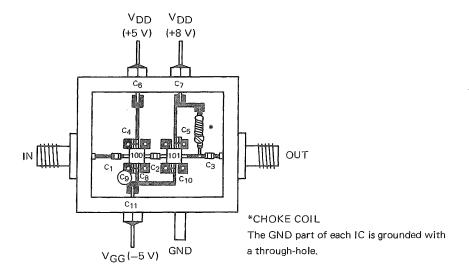

Fig. 12 and 13 show the circuit diagram for this amplifier and the bias circuit example, respectively.

Fig. 12 Circuit Diagram of  $\mu$ PG100B/ $\mu$ PG101B Cascade Connection Amplifier

Fig. 13 Bias Circuit Example

IC<sub>1</sub>: 3-pin regulator  $\mu$ PC78N08 IC<sub>2</sub>: 3-pin regulator  $\mu$ PC78N05

IC3: Intercil ICL7660

$\mu$ PG100B requires V<sub>DD</sub> +5 V and V<sub>GG</sub> -5 V as the supply voltage;  $\mu$ PG101B requires V<sub>DD</sub> +8 V and V<sub>GG</sub> -5 V. (V<sub>GG</sub> can be used in common for both  $\mu$ PG100B and  $\mu$ PG101B.)

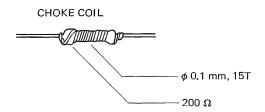

$V_{DD}$  is applied to  $\mu PG101B$  using the external choke coil. The DC block capacitors are inserted into input/output of  $\mu PG100B$  and  $\mu PG101B$ , and these ICs are connected with the 50  $\Omega$  microstripline.

To compose this circuit, take special care to the following points:

(1) If the air-core coil is used as the choke coil for  $\mu$ PG101B, coil Q becomes too high and may resonate with the stray capacity, causing a dip in the band. To avoid this, coil Q should be dumped by the resistor of about 200  $\Omega$  in advance.

The circuit diagram shown in Fig. 12 is recommended to be used.

(2) As the multi-stage amplifier gives high gain, if ripple of power supply is present on the V<sub>GG</sub> side, it is amplified and causes the output waveform to be amplitude-modulated. An electrolytic capacitor should be used to remove this ripple.

As shown in Fig. 13, the bias circuit can be easily composed by using the 5 V and 8 V 3-pin regulator for  $V_{DD}$  and converting +5 V into -5 V with the DC-DC converter for  $V_{GG}$ .

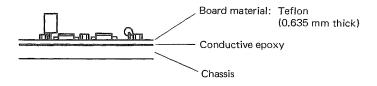

Fig. 14 shows the printed pattern example and the assembly method. In this figure, the teflon board of 0.635 mm thickness is soldered to the chassis with conductive epoxy (silver paste), all the parts are mounted on the board surface, and the GND part of each IC is grounded with a through-hole.

Fig. 14 Assembly Method

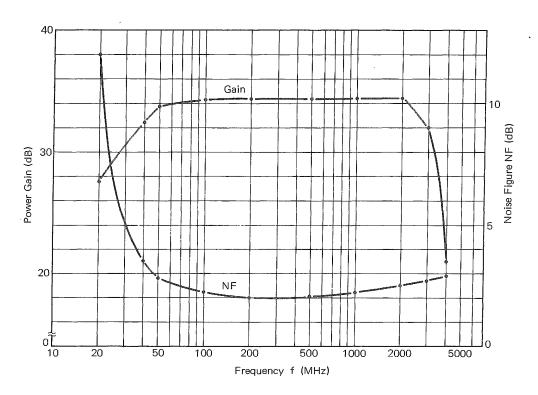

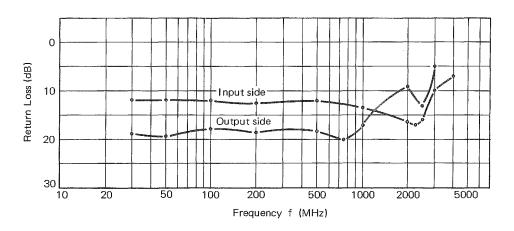

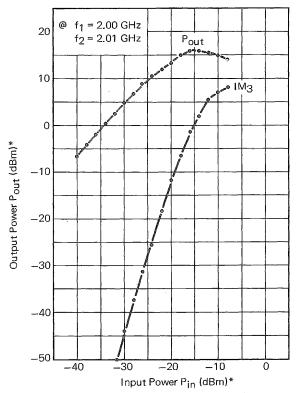

Fig. 15 through 18 show the characteristics of the amplifier composed as described above. Summary of test result is shown as follows:

- Gain: 32 dB or more (@ 50 to 3 000 MHz)

- NF: 2.8 dB or less (@ 50 to 3 000 MHz)

- Input return loss: 10 dB or more (@ 50 to 3 000 MHz)

- Output return loss: 5 dB or more (@ 50 to 3 000 MHz)

- $P_{O(1 dB)}$ : +18 dBm or more (@ 50 to 3 000 MHz)

- IM<sub>3</sub>: 37 dBc @  $f_1$  = 2 GHz,  $f_2$  = 2.01 GHz, Output level of +10 dBm for each wave

- 3-dB frequency band width: 34 to 3 100 MHz

Fig. 15  $\mu$ PG100B/101B Gain and NF vs. Frequency

Fig. 16  $\mu$ PG100B/101B Return Loss vs. Frequency Characteristics

Fig. 17  $\mu$ PG100B/101B  $P_{out}$ - $P_{in}$  Characteristics

Fig. 18  $\mu$ PG100B/101B  $P_{out}$ - $P_{in}$  Characteristics

# 5. CAUTIONS FOR USE

- (1) Take great care to protect against static electricity because the GaAs MES FET is used as a basic cell in the IC. Be sure to ground the work bench, your body and soldering iron, and use a metal tray for storing the products.

- (2) The package cap is adhered with AuSn. Therefore, be sure to perform soldering at temperatures under  $260\,^{\circ}\text{C}$  for 10 seconds or less.

Be careful that the lead wires are shortcircuited via the AuSn part when solder is put into contact with the AuSn part.